# Mod2mag User's Manual

Nicolas Paris<sup>1</sup>

November 8, 1991

<sup>1</sup>Laboratoire d'Informatique de l'Ecole Normale Supérieure URA 1327 du C.N.R.S.

# Acknowledgements

I am very grateful to Pr. Bertrand Zavidovique who trusted me for such a large work.

I wish to thank Thierry Bernard, Georges Quenot, Ronan Keryell and Jean-Dominique Gascuel for their help and suggestions.

Last but not least, I give Philippe Hoogvorst special thanks for the time he has spent checking this document.

# Chapter 1

# Introduction

# 1.1 Presentation of Mod2mag

**Mod2mag** is the masterpiece of the VLSI compilation environment developed at the Computer Science Laboratory of the Ecole Normale Supérieure. This document is mostly dedicated to the description of **mod2mag**. However a manual page is available (mod2mag(1)) to summarize the flags of **mod2mag**. This environment is a complement of the Magic Software Distribution of the University of California at Berkeley. File formats are compatible with the formats of the **magic** tools. It is necessary for the reader to read the manual of the Berkeley distribution in order to understand this document.

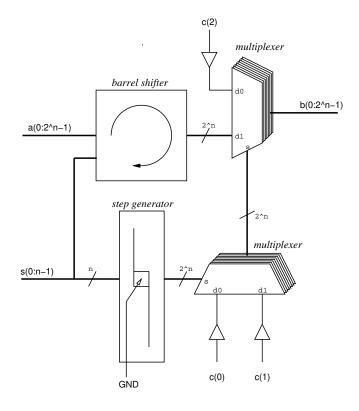

**Mod2mag** is a silicon compiler. It takes input files in the syntax of the **model** language and may generate different kinds of output:

- Transistor level netlists for electric simulation,

- Switch-level/logical/behavioral netlists for multi-level simulation,

- Layouts for magic,

- Layout netlists for the magic router,

- Pcb netlists for the Dedale2000 pcb router.

Mod2mag uses basic layout tiles which are designed with magic.

Being very efficient for the development of small cells, the **magic** environment does not provide any efficient facility to convert a schematic description into a layout hierarchy. **Mod2mag** has been developed to tackle this problem. In this environment:

- Magic is used to design basic library cells,

- Mod2mag is used to describe, simulate and debug schematics and finally to generate the layout, and the PCB netlists.

Mod2mag allows to follow a top-down methodology due to the behavioral description of the cells. It is associated with msim for the multi-level simulation. Our model syntax can be classified in Hardware Description Language. Furthermore, it provides facilities to develop parametrical libraries in order to generate layout in both full-custom and/or standard cell style.

# 1.2 Libraries, examples and technologies

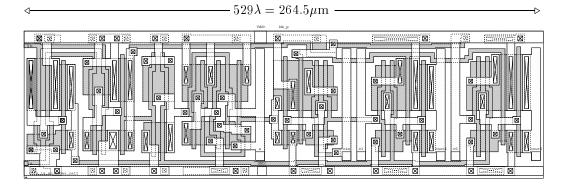

Associated with the **Magic** environment, this environment is efficient for the design of VLSI. The last problem is the development of libraries in the designer technology. Tools and methodologies are provided in order to help a designer or a local maintainer to develop custom libraries in a local technology. This distribution is associated with layout libraries in 2 technologies:

- the mcmos technology which corresponds to the ECDM20-C 2μm Cmos technology of European Silicon Structure. A specification of the standard cells for this technology is provided in the appendix A. Libraries and examples are provided in the software distribution in the directory ~cad/ulm/mcmos.

- the ecpd technology which corresponds to the ECPD15  $1.6\mu$ m Cmos technology of European Silicon Structure. A specification of the standard cells for this technology is provided in the appendix B. Libraries are provided in the software distribution in the directory "cad/ulm/ecpd. This technology is scalable (unless for pads which must be adapt to the technology). So it is relatively easy to develop a technology in the existing ECPD12  $1.2\mu$ m Cmos technology of European Silicon Structure and to the ECPD8  $0.8\mu$ m Cmos technology to come of European Silicon Structure.

The appendix C explains to the local maintainer how to develop a new environment for a new technology.

# **1.3** Presentation of the global environment

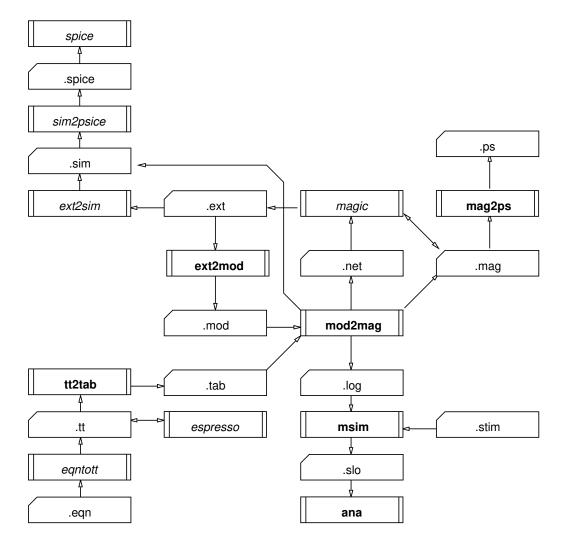

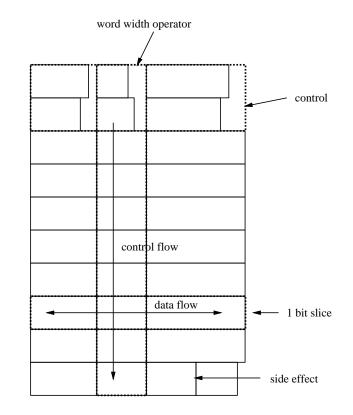

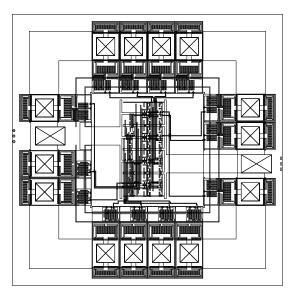

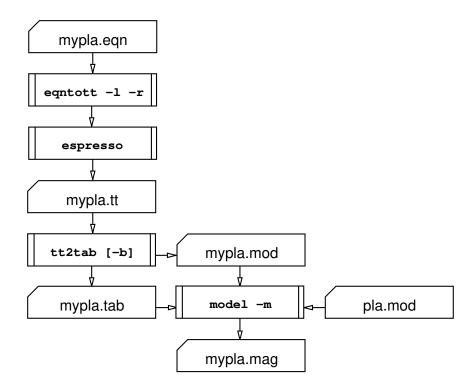

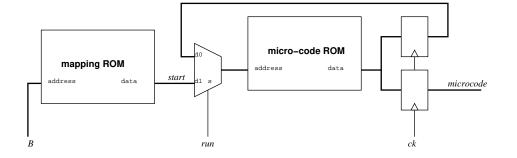

The figure 1.1 shows the data flows between files and program for the whole environment. Programs in bold face belongs to our distribution while programs in italic belongs to the Berkeley environment.

### 1.3.1 File formats

File formats are identified by the extension of the of each file:

- the .mod files are text files which contain the source for mod2mag. They follow the syntax of the model language. This document precisely describe the syntax and the semantic of this format..mod files can be generated by ext2mod from .ext files.

- the .mag files are layout files, which contains the graphical hierarchical description of the layout cells. This format is the magic(5) format. .mag files are generated by mod2mag and can be edited by magic.

- the .ext files are hierarchical netlist files. They describe under a hierarchical format the transistor netlist of a circuit. They are generated by magic and are use by ext2mod and ext2sim. This format is described in ext(5).

- the .net files are netlist for the magic router. It may be generated by mod2mag. This format is described in net(5).

- the .sim files are flat electrical netlist. This format is described in sim(5). These files are generated by mod2mag or by ext2sim.

Figure 1.1: software environment

- the .al files are netlist alias files. This format is described in sim(5). These files are generated by mod2mag or by ext2sim. They describe the different names given to the same wires. They are associated with electrical flat netlists (.sim) or logical flat netlists (.log). These files are used by msim and sim2spice.

- the .spice files are electrical flat netlists for spice. These file are generated by sim2spice.

- the .log files are logical flat netlists. This format is described in log(5). These files are generated by mod2mag. They are read by msim.

- the .beh files are behavioral flat netlists. This format is described in msim(1). These files are generated by mod2mag. They are read by msim.

- the .stim files are stimuli for multilevel simulation. The format is described in msim(1). These are manually edited text files. They are read by msim.

- the .slo files hold the wave-forms generated by msim and displaid by ana. The format is described in slo(5).

- .eqn files hold the equation of PLAs. They are text files edited manually. This format is described in equtott(1). They are converted into .tt format using equtott.

- the .tt files are table description of PLAs. They are generated by eqntott from .eqn files. They may be optimized by the espresso program. The format is described in espresso(1).

- the .tab files are PLA files. They can be read by the Read command in model. It may be generated by tt2tab from the .tt files.

- the .ps files are the Postscript files. The program mag2ps converts .mag cells into printable Postscript files. Ana provide also .ps files to plot the wave-forms.

# 1.3.2 Programs

Our distribution consists of the following programs:

- mod2mag is the silicon compiler. It takes as input .mod files and .tab files and generates layouts (.mag), routing netlists for magic (.net), electrical netlist (.sim and .al) and multi-level simulation netlists (.log, .beh and .al). This document is dedicated to the description of this program. However a manual page is available (mod2mag(1)).

- ext2mod generates a model interface and a data sheet for every .mag cells. This program is documented in ext2mod(1).

- msim is the multi-level simulator. It as input takes a multi-level netlist as input(.log,.beh and .al) and stimuli(.stim). This simulators is documented in msim(1).

- ana is the wave-form analyser/model-debugger. This program is documented in ana(1). It reads .slo files and may produce Postscript files.

- mag2ps generates Postscript print out of layout cells. This program is documented in mag2ps(1). All the layout figures of this document have been generated by mag2ps.

- tt2tab converts .tt format to a format readable by this program.

The manual pages for all these programs and the new file formats are located in "cad/ulm/man and in the appendixF.

# 1.3.3 Organization of this document

This document follows this plan:

- the next chapter presents the syntax of the language model,

- the chapter 3 presents the simulation aspects,

- the chapter 4 presents the layout generation aspects,

- the first 3 appendices presents the specification of cells for two technologies and how to develop a new technology.

- the appendix D presents the data sheet of the library in the mcmos technology.

- the appendix E presents small, though non trivial circuits generated by mod2mag.

- the last appendix contains the manual pages of the programs and file formats of the distribution.

# Chapter 2

# Getting Started

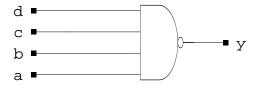

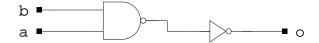

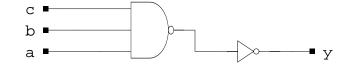

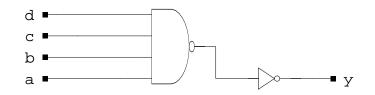

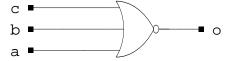

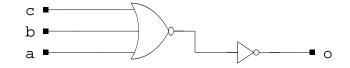

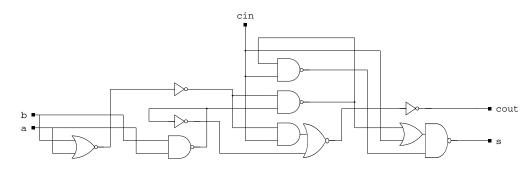

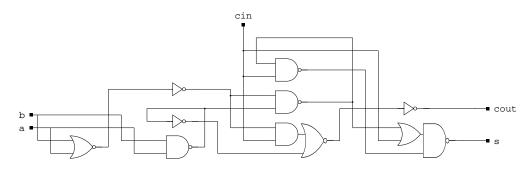

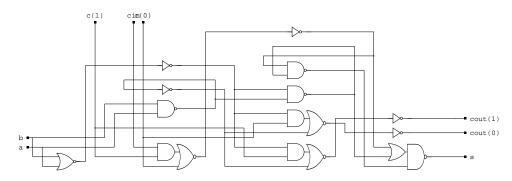

This chapter is dedicated to the presentation of the syntax of **model**. The design of different levels of implementation of a *nand* gate will be an opportunity to illustrate the syntax of **model** and the associated semantic.

# 2.1 Preparing an input file

Files expressed in the **model** syntax possess usually the ".mod" extension. An input file is mainly made up of two kinds of statements:

- declarations and definitions of objects,

- instances of these objects.

The order of these declarations/definitions and instances is irrelevant, as long as objects are declared or defined before being used.

# 2.2 First lesson : the basic syntax

Table 2.1<sup>1</sup> shows the first implementation of our **nand** gate. At the first line, a library file is included. The **Include** statement is the priviliged way of sharing objects and/or libraries between different designs: it is possible to build and share libraries. These included files are read as if their contents take place directly in the calling file. As a single file for each library is included in various designs, the coherence between them is automatically ensured.

Here, the magicdef.mod file is assumed to contain the definitions of the ntrans and ptrans objects. Between line 3 to line 12, the nand gate is defined. At line 17, this gate is used.

# 2.2.1 Definition and instance of Parts

The main purpose of the **model**language is to provide a syntax for the description of pieces of hardware. Circuits are often described with a hierarchy of cells. Cells are built with electronic

$<sup>^1</sup>$ lesson1.mod

```

Include "magicdef.mod"

1

{ description of a nand gate with two inputs in(0:1)

2

Part nand[in(0:1)] -> out

3

4

Signal middle

5

6

ntrans(1000,200)[in(0)] -> GND,middle

7

ntrans(1000,200)[in(1)] -> out,middle

8

9

ptrans(1500,200)[in(0)] -> Vdd,out

ptrans(1500,200)[in(1)] -> Vdd,out

10

11

12

End

13

14 Signal a,b

15

Signal output

16

nand[a,b] -> output

17

```

Table 2.1: the nand gate : first implementation

component like fet transistors and capacitors and with subcells. Every cell is called a *part* in the **model**terminology.

The definition of the nand gate looks like the definition of a function. It begins with the **Part** keyword and ends with the **End** keyword. Each enclosed statement belongs to the nand definition. The next word is the name of this part, followed the different parameters of this "function":

- an optional list of integer parameters, enclosed between parenthesis. An empty list is illegal and must be omitted;

- a list of input signals surrounded with square bracket "[]" (here the bus in(0:1));

- a list of output signals (located after an arrow "->"). When the output list is empty, the arrow must be suppressed

Mod2mag provides electrical rule checking which is not based on the distinction between inputs and outputs in a part declaration. (the Electrical Rule Checking mechanism is described in chapter 3). This distinction exists only for legibility purpose. Anyway, we must handle signals which are not really well-typed. For instance, the source and the drain of a FET transistor are neither input nor output. By convention, the irresolute input/output signals take place into the part output list, as shown in our first example for the instances of ntrans and ptrans, which are FET transistors.

These instances show examples of the use of integer parameters (which represent here the width and the length of the transistor channel in hundredths of micron).

### 2.2.2 Signals and buses

Wires are required for connecting the different parts together. A wire may be known under several names. These names are called *signals* in the **model** syntax. They must be declared before being used. The **Signal** keyword declares signals in the current context:

- local signals in the body of a part declaration (e.g. middle at line 5),

- global signals in the top level of the file (e.g. a, b and output at lines 14 and 15)

Parameter signals are implicitly declared in the header of a part definition: so the signals in(0), in(1) and out are declared in the current part by in(0:1) and by out in the header of the part definition (at line 3).

An easy way to declare a list of signals is to declare a bus which is an array of signals. An index mechanism allows to extract signals from a bus. The domain of this index must be specified at the declaration of the bus with its limits separated with column (:) and enclosed with parenthesis. So,

```

Signal data(0:4)

```

declares a bus consisting of 5 signals: data(0), data(1), data(2), data(3) and data(4). A given identifier can take place in only one signal declaration in a given context. For instance, it is illegal to write:

```

Signal data, data(0:4), data(7:11)

```

When using a bus, it may be useful to extract a subbus from this bus, or to build a bus from signals and subbuses.

## 2.2.3 Construction of signal lists

Different constructors are available to build list of signals:

• the most simple operator is the signal list concatenation. This operator is the comma (","). If a, b and c are signals or buses, then a, b, c is a list of signals. The first way to list every signal of the data bus is to write directly:

data(0), data(1), data(2), data(3), data(4)

It is possible to share in a list the identical bus name: data(2),data(1) ⇔ data(2,1)

It is possible to apply a list of integers to a bus as long as every integer belongs to the range of the bus: it results a signal list. By this mechanism, we can use every integer list constructor for signals list. The second way to list every signals of the data bus is to write:

data(0,1,2,3,4)

It is possible to specify a regular enumeration of integers with the colon operator (":").

1:5 is a list of those five integers 1, 2, 3, 4, 5. We may also specify a step. 6 : 1

By -2 is a list of the three integers 6, 4, 2. The third way to list every signal of the data bus is to write:

data(0:4)

• Sometimes, every signals of a bus must be listed in the natural order. The name of the bus without any parenthesis is enough to describe the whole signal list. The most simple

| type   | name   | tension |

|--------|--------|---------|

| ground | Ground | 0V      |

|        | Gnd    | 0V      |

|        | Earth  | 0V      |

|        | Zero   | 0V      |

|        | Vss    | 0V      |

| power  | Power  | 5V      |

|        | Vdd    | 5V      |

|        | Vcc    | 5V      |

|        | One    | 5V      |

Table 2.2: power-supplies special signals

way to list every signals of the data bus is: data

# 2.2.4 Special signals: the power-supplies

Power supplies signals are special global signals in **model**. These global signals are known by the software. Their names are keywords. There exist 2 power supplies: the ground (0V) and Vdd (5V). the table 2.2 shows the multiple names given for each power-supplies.

When required, it is possible to built power-supplies buses : Vdd(1:4).

### 2.2.5 Keywords

We have yet discovered some keywords: Part, End, Signal, Vdd and GND. A word beginning with an upper-case letter must be a keyword. The rest of the word is not case-sensitive : Part and PART are equivalent.

# 2.2.6 Identifiers

A word beginning with a lower-case letter is an identifier. Unlike keywords, the identifiers are case-sensitive: clock and clocK are not equivalent. Identifier names are made up of characters (with no limitation on the number) chosen among letters, digits and the underscore character ("\_"), with the classical convention that the first character is not a digit.

# 2.2.7 Various lexical elements

Instructions are delimited by one or more carriage returns (<CR>). The carriage return is meaningless after a comma (,), an arrow (->), or one of these keywords Then, Else, And and Or. It is possible to cut a too long line with the character minus (-) placed just at the end of the line.

Comments start with a curly bracket ({) and stop at the end of the line.

Strings are surrounded by double quotes ("). Double quotes, carriage returns, tabulations, backslashes are expressed in a string by  $\",\n,\t$  and  $\$ .

# 2.2.8 Compiling a model file

# Configuration

In order to compile the examples of this manual, you need to add the directory ~cad/bin to your environment variable PATH. It is also better to create your own directory, where to run the examples. You have two files to copy in this directory:

- ~cad/ulm/mcmos/example/.magic

- ~cad/ulm/mcmos/example/lesson1.mod

The .magic file specifies where to find the layout cells (.mag) and the model files (.mod). This file contains magic orders, which are executed at the beginning of a magic session (see magic(1)). It is necessary to specify where to find the cells thanks to the path command. This file is also interpreted by mod2mag only to read eventual path command. Programs (magic and mod2mag) successively read the optional files:

- ~cad/lib/magic/sys/.magic,

- ~/.magic,

- ./.magic.

The last path command defines where to find the cells and the model files. Our .magic file contains the command:

```

path ":.: ~cad/ulm/mcmos/example: ~cad/ulm/mcmos/lib8: ~cad/ulm/mcmos/pad: ~cad/ulm/mcmos/pla:"

```

which indicates that  $\mathbf{model}$  files and layout cells are successively searched in :

- . the current directory,

- ~cad/ulm/mcmos/example the example directory,

- ~cad/ulm/mcmos/lib8 the cell library,

- ~cad/ulm/mcmos/pad the pad library,

- ~cad/ulm/mcmos/pla the pla library,

As the example directory takes place is the path command, you need not to copy the lesson1.mod file, but it is better for you to have your own copy of the file if you want to modify it.

### Running the compiler

To compile the example, run the following command:

```

model lesson1.mod

```

or

```

model lesson1

```

The compiler generates one of those 2 files:

• lesson1.err which contains the errors of the file (if any).

```

Include "magicdef.mod"

1

2

Part nand(n)[in(0:n-1)] -> out

3

4

5

Signal middle(0:n)

6

Integer i

7

8

If n > 10 Then

9

Error "too many inputs : ",n," in the nand gate"

10

Endif

11

Message "warning nand: ",n," inputs > 5" If n > 5

12

13

middle(0) -> GND

14

15

For i=0:n-1 Cycle

ntrans(1000*n,200)[in(i)] -> middle(i),middle(i+1)

16

ptrans(2000,200)[in(i)] -> Vdd, out

17

Repeat

18

19

middle(n) -> out

20

21

End

22

23

Constant size = 4

24

25

Signal input(1:size)

26

Signal output

27

28

nand(size)[input] -> output

```

Table 2.3: the nand gate : second implementation

• lesson1.out which is the interpreted output of the compiler, if the design description is coherent (if not correct).

When **mod2mag** is called without any flags, only the correction of the input file is checked. We will discuss in the next two chapters the differents that can be set and the different output files generated. In this chapter, we pay attention only the basical syntax of **model**.

# 2.3 Second lesson : more about the basic syntax

Let us write now a more general *nand* (table  $2.3^2$ ). We want to express in a single part definition how to build **nands** with 2, 3, 4 and so on inputs. We need integer identifiers, arithmetic operators and parameterized calls. This example is the opportunity to discuss the following points:

$<sup>^{2}\</sup>mathrm{file}\,\mathtt{lesson2.mod}$

- Declaration and use of integers,

- Flow control,

- Debugging messages.

## 2.3.1 Integers

Integers are used in **model** as in any programming language. They can have an integer value assigned to, together with integer constants in arithmetical/logical expressions. Last but not least, they can be passed by value as parameter to functions.

#### Integer identifiers

Integer identifiers have the same lexical form as the signals identifiers. It is legal for a signal and a integer to have the same name <sup>3</sup>. Arrays of integers can be declared and used as arrays of signals (= buses).

#### Integer lists

Integer lists can be constructed using the same syntactical constructs as the list of signals: Integer i(0:6), j,k

successively declares an array of the 7 integers i(0),...i(6) and 2 integers j and k. The instances of integers is identical to signals ones. i(5:1 By -2) means the integer list i(5), i(3), i(1).

In the same manner as a signal, an integer identifier can be either local to a part (i.e. declared between the **Part** header and the corresponding **End** statement) or global (.i.e declared outside of any definition of a part).

#### Integer initialization

Each global variable is initialized at the null value, unless another value is given in the command line of the **model** program. The line 23 of our example could be changed by:

```

Integer size

size = 4 If size = 0

```

By default, size gets the 0 value at its declaration, and is then modified to get the 4 value. If we compile this example with the **model** command:

```

model size=3 lesson2.mod [other options]

```

size is initialized to 3. This mechanism is convenient to parameterize the compilation without modifying the **model** source.

#### **Constant integer identifiers**

A convenient way to use numerical constants is illustrated at line 23 of the example 2.3. The corresponding identifiers ("size" in the example tab. 2.3) cannot be modified after its declaration.

<sup>&</sup>lt;sup>3</sup>This should be avoided for legibility!

| operator | arity | function                        |

|----------|-------|---------------------------------|

| +        | 2     | addition                        |

| _        | 2     | subtraction                     |

| _        | 1     | unary minus                     |

| *        | 2     | $\operatorname{multiplication}$ |

| 1        | 2     | euclidean division              |

| %        | 2     | modulo                          |

| &        | 2     | logical and                     |

| !        | 2     | logical or                      |

| !!       | 2     | exclusive or                    |

| <<       | 2     | shift left                      |

| >>       | 2     | arithmetical shift right        |

| \        | 1     | to 1's complement               |

| ^        | 2     | exponentiation                  |

Table 2.4: the integer operators and their arities

#### Numerical constants

Numerical constants are expressed by default in decimal base or in any other base from 2 to 36. If the base is not decimal, the value of the base in decimal is concatenated to left of the numerical constant with an underscore (\_) as separator. When the base is greater than 10, the missing "digit" to build the number are taken from the alphabet (case-unsensitive). So 'a' represents 10, 'b' represents 11 and so on until 'z'. For example 123, 16\_C, 2\_1101 represent the decimal values 123, 12, 13.

#### Integer expressions

Integer expressions are built like in programming languages. The table 2.4 presents the different integer operators with their arities.

The precedence of operators is processed among this order:

- (unary) and \,

2. ^,

- 3. \*, / and %,

- 4. + and -,

- 5. << and >>,

- 6. **&**,

- 7. ! and !!.

Parenthesis are used to force the precedence. Each binary operator is left associative.

| operators | function              |

|-----------|-----------------------|

| =         | equal                 |

| #         | different             |

| <         | less than             |

| >         | greater than          |

| <=        | less than or equal    |

| >=        | greater than or equal |

Table 2.5: comparator functionality

# 2.3.2 Flow control

Flow control is useful to express the construction algorithms of parts. There are 6 kinds of flow controls:

- 1. conditional control If,

- 2. endless loop control Cycle.

- 3. enumeration control For,

- 4. conditional ended loop control While,

- 5. conditional ended loop control Until,

- 6. case switch control Switch.

Exit and Continue are used to modify the execution of the flow. Some of these flow controls need conditions. They are expressed by boolean expressions.

#### **Boolean expressions**

Basic booleans are comparisons between integer expressions. Then, they can be made up of boolean operators to build more complex boolean expressions.

**Comparators** A comparator admits two integer arguments as input and returns a boolean. The table 2.5 presents these different comparators with their respective functionality.

#### Boolean operators (And, Or and Not).

The operator precedence follows this order:

- Not,

- And,

- Or.

#### If: conditional execution of statements

The complete syntax of the If statement is:

If condition Then

$statement\_list\_1$

Else

statement\_list\_2

Endif

The boolean expression is first evaluated. If the value is true, the  $statement\_list\_1$  is executed and  $statement\_list\_2$  is skipped. Otherwise  $statement\_list\_1$  is skipped and  $statement\_list\_2$  is executed. If the second statement list is empty, the **Else** keyword is not necessary. The example 2.3 shows this construction between lines 8-10.

This heavy construction can be shortened when the first statement body has only one statement and when the second statement body is empty:

statement If condition

Program 2.3 shows an example this construction at line 12.

#### Iteration statements

There is a general construction to express the body of some loop:

Cycle

statements

Repeat

In the body statement, the **Continue** statement jumps to the next iteration of the loop and the **Exit** statement jumps out of the loop.

The iteration statement described above will never end unless an exit statement is executed. Apart from explicitly programming an exit, there are 3 ways of controlling loops.

• The For statement will repeat the execution of the loop body while the control variable is successively assigned the values of a list of integers. The loop is terminated when the list is exhausted. Syntax:

For variable = integer list Cycle statements

Repeat

• The While statement evaluates a boolean condition to continue the iteration:

While condition Cycle statements

Repeat

The condition is first evaluated. Then if the boolean value wass true, the body of the loop is  $executed^4$ .

• The Until statement also uses a boolean to control the loop. Unlike the While statement, the loop body is first executed<sup>5</sup>. Then the condition is evaluated. The body of the loop is executed once more if the boolean is false. Syntax:

Cycle

statements

<sup>4</sup>It may be executed 0 times.

<sup>5</sup>It will be executed at least once.

#### Repeat Until condition

Exit and Continue are still available with these 3 ways of controlling loops.

#### Case statements

The Switch statement allows to choose between multiple possibilities

#### For : enumeration control

The For statement is classically used in progamming languages to execute a statement body for each elements of a enumeration of an index.

A list of values for the variable is provided, instead of the range of variation:

#### For variable = integer list Cycle

statements

Statements are evaluated for each element of the list. At each evaluation *variable* is set to the value of the next integer of the list. The content of the list is evaluated before entering the loop. This mechanism is more flexible thanks to the lists construction. In our example 2.3 lines 15-18, a classical range is used with to the enumeration (:) operator for list construction.

As for the If statement, it is possible to shorten the notation, when a single statement is involved in the body of the For loop:

statement For variable = integer list

The For loop execution can also be modified by the Continue and Exit operators.

#### While : conditional ended loop control

The Cycle loop can be legibly written with either the While or Until constructions. It indicates when to stop the execution of the loop with a boolean expression. The boolean can be evaluated before (While) or after (Until) the body of statements.

The While statement syntax: While condition Cycle

statements

The condition is evaluated at every iteration of the statement body. If the test is passed, the execution continues inside the loop, otherwise the execution resumes after the end of loop. The For construction between line 15 and 18 can be rewritten:

```

i = 0

While i < n Cycle

ntrans(1000*n,200)[in(i)] -> middle(i),middle(i+1)

ptrans(2000,200)[in(i)] -> Vdd, out

i = i+1

Repeat

```

The Until statement syntax:

Cycle statements

Repeat Until condition

The condition is evaluated after every evaluation of the body statements. If the test is passed, the execution continues to the next statement after the end of loop, otherwise jumps back to the start of the loop.

The While and Until loops execution can be also modified with the Continue and Exit operators.

#### Switch : case switch control

The Switch statement is useful to choose a sequence of statements between several sequences depending on the value of an expression. The structure of the Switch statement is:

```

Switch expression

Case expression1

statement list 1

Case expression2

statement list 2

...

Default

statement list n

```

End

It roughly works as the C switch. The *expression* is evaluated at the entrance of the switch statement. For each Case statement the calculated value of *expression* is compared to the evaluation of the associated expression (*expression1*, *expression2*,...). At the first time the expressions are equal, the statement lists following the Case statement are executed until the first Exit execution. The statements following the Default keywords (if it exists) are executed if no equality has been formerly found.

# 2.3.3 Signals merging

As it can be observed in line 14 and 19 the arrow operator (->) is used to connect signals. Different names can refer to the same wire). This connection can merge directly a signal list (possibly of one element) to another one of same size. The different names for an equipotential are equivalent: the arrow operator is commutative (unlike the assignment operator).

#### Instance mechanism

The expression ptrans(2000,200)[in(i)] (line 17) defines an instance of ptrans with the integer parameters 2000 and 200, with in(i) as an input bus and returns the list of the output signals of the instance which must be connected. The arrow operator completes this task by connecting the corresponding signals to Vdd and out. It is only a legibility convention to put the instance at the left of the arrow. When a instance has no output, the right side of the arrow is empty. In this case the arrow must suppressed.

#### Unconnected signals

Sometimes, some of the outputs are unused. Because of the instance mechanism, the designer must specify a signal for each output. It is tedious to define ghost signals for each unconnected output: the operator "unconnected" -- allows us to define an unnamed unconnected signal. It

acts like a dummy symbol generator. Because many signals may be unconnected in a signal list, it is possible to define an unconnected bus: --(0:7) is a bus of 8 unconnected signals.

# 2.3.4 Debugging messages

Model provides messages for debugging facilities. There are two kinds of print statements:

- Message/Messagef : print and continue compilation,

- Error/Errorf : print and abort compilation,

These statements have the following syntax:

Message list of strings and integer value Messagef "string format" list of strings and integers Error list of strings and integer value Errorf "string format" list of strings and integers

In the Message/Error statements, strings are printed literally and integers are converted to their decimal representations. For the Messagef/Errorf statements, the first parameter is a format string. The syntax of this format is the same as C's (see printf(3)).

# 2.4 Third lesson : last refinement about the syntax

To end our fast sight of the **model** syntax, let us consider our third implementation of the nand gate (table  $2.6^6$ ).

```

Include "magicdef.mod"

1

2

3

Part basic_nand[in(1:*)] -> out

4

Integer n,i

5

n = Length[in]

6

Signal middle(1:n+1)

7

8

middle(1) -> GND

9

For i=1:n Cycle

10

ntrans(1000*n,200)[in(i)] -> middle(i),middle(i+1)

ptrans(2000,200)[in(i)] -> Vdd, out

11

12

Repeat

middle(n+1) -> out

13

14

15

End

16

17

Part basic_nor[in(1:*)] -> out

18

Integer n,i

19

n = Length[in]

20

Signal middle(1:n+1)

21

middle(1) -> Vdd

22

23

For i=1:n Cvcle

ptrans(2000*n,200)[in(i)] -> middle(i),middle(i+1)

\mathbf{24}

ntrans(1000,200)[in(i)] -> GND, out

25

26

Repeat

27

middle(n+1) \rightarrow out

End

28

```

<sup>6</sup>in file lesson3.mod

```

29

30 Part basic_or[in(1:*)] -> out

31

basic_nor[basic_nor[in]] -> out

32

End

33

34 Part nand[in(1:*)] -> out

35

Integer n,p,j,first,last

36

n = Length[in]

37 Signal middle(1:3)

38

39

If n < 5 Then

{ recursion terminaison }

basic_nand[in] -> out

40

41

Else

p = Sqrt(n)

42

43

p = 3 If p > 3

44

first = 1

45

For j=1:p Cycle

last = first + (n - 1)/p

46

last = n If last > n

47

48

nand[in(first:last)] -> middle(j)

49

first = last+1

50

Repeat

basic_or[middle(1:p)] -> out

51

52 Endif

53 End

```

Table 2.6: the nand gate : third implementation

This example provides the opportunity to study the next features:

- use of \* as implicit parameter,

- built-in functions and procedures,

- recursivity.

# 2.4.1 Use of star (\*) as implicit parameter

At line 3 of the last example, a star (\*) appears in the input signal list of a part definition. This star represents a number which is in fact a parameter of the part. The value of the star is dynamically calculated when the part is instanced, so that the length of the list of input formal parameters matches the length of the actual input parameters.

The value of the star is an implicit parameter of the part. It is necessary to get the size of the bus containing the star. The Length operator achieves this task. It takes as input a list of signals (typically the bus containing the star) and yields an integer which is the length of the list:

Length[a,b(1,3,5),c(0:2),d]

returns 8. If an input bus is declared as in tab. 2.6 line3, the length operator applied to the bus will give the value of the  $*^7$ .

<sup>&</sup>lt;sup>7</sup>If the bus is declared b(0:\*), Length[b] will yield the width of the bus, which is the value of the star plus 1.

## 2.4.2 Built-in functions and procedures

Built-in functions and procedures (like Length) are provided to deal with parameters, to compute maths functions and to read files.

# 2.4.3 Log function

The Log function is convenient to calculate the number of buffering stages of an inverter. The Log function takes a single parameter p and returns the smallest integer n such that  $2^n \ge p$ . For instance:

Log(15) = 4Log(16) = 4Log(17) = 5

It is used at line 68 of table 4.4 page 50 for a multistage inverter generator.

### 2.4.4 Sqrt function

The Sqrt function is convenient to develop an amplification tree of depth 2 with load repartition. The Log function takes a single parameter p and returns the smallest integer n such that  $n^2 \ge p$ . For instance:

```

Sqrt(3) = 2

Sqrt(4) = 2

Sqrt(5) = 3

```

It is used at line 42 of table 2.6.

#### 2.4.5 Input functions

In order to import a large number of parameters into **model**, which could not be easily expressed through the **model** syntax, file reading mechanisms are provided. As more than one files can be read simultaneously, each opened file is identified by a unique integer number. This number (from 0 to 19) is returned by the **Open** function which takes one parameter: the name of the file.

```

descriptor = Open "filename"

```

The **Read** function reads the next integer in the file pointed by a descriptor. **Read** takes one integer parameter (the file descriptor) and returns the value of the next integer read from the file. It is assumed that integers are written in decimal, one by line. A line in the file which begins with a star is treated as a comment and is skipped. If the line start with a star, it is skipped (because it is a comment).

The Close procedure releases the file descriptor in order to be used again. It admits the descriptor as unique parameter.

## 2.4.6 Recursivity

**Model** parts can be recursive. The recursion is always based on integer parameters. In the example presented in table 2.6, the **nand** part is recursive (on the value of the hidden parameter star). Recursivity is essential to express easily complex structures like trees.

## 2.4.7 How to debug complex files?

The integer parameters and the recursivity allow to develop very powerful objects. The price of this power is the complexity of the debug. We require some help to debug easily **model** files.

When a model file has been created, it must be checked. The command:

model file

compiles it. Without any flags, the software only checks the input file and evaluates it.

The compilation for **model** consist in fact in the evaluation of integer expressions. Compilation time errors are of two types:

- syntax errors,

- evaluation errors.

The compilation process has two passes.

The first one parses the **model** input file and checks the syntax. An internal representation of each object is then built. In this representation, no evaluation is done. In the first pass, the symbols are checked (declaration before instance). These errors are easy to correct because error messages are explicit and point out the implied lines.

At the second pass, this representation is interpreted. At this stage, errors may occur:

- arithmetical errors: divide by 0, negative arguments for Sqrt and Log.

- range errors: overflow and underflow of arrays and buses,

- mismatches in signal list connections: wrong number of input signals, bus size mismatch in bus connections.

- non-existence in the upper contexts of inherited signals.

These errors are also easy to correct. Using Message, it is possible to trace integer values and to detect what is wrong within the input file.

When the file is apparently correct (there is no more compilation time errors), the file can be observed as correct for the point of view of the software: the input file is consistent; it is correct from the compiler view point. There is no more ".err" file and a ".out" file is created.

The ".out" file contains the interpreted view of the input design in model syntax. No integer and no flow control structure subsist. This view of the design conserves its hierarchical structure. It is the reference of the exact structure of the design.

# 2.5 Fourth lesson : scope of signals and integers

# Chapter 3

# Description for the simulation

One of the purposes of an Hardware Description Language like **model**, is to describe the electrical interconnection of a circuit. The language must contain the information required by the software to make some electrical verifications (Electrical Rule Checking) and to extract the following different data:

- transistor simulation netlist,

- gate and behavioral simulation netlist,

- routing netlist for chip router

- routing netlist for PCB router.

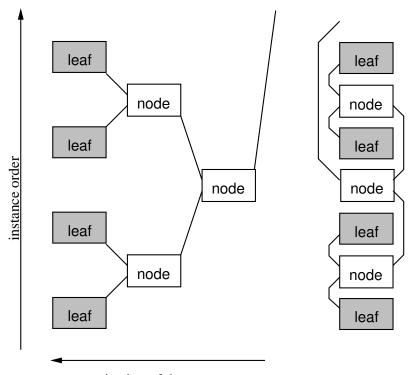

The last two points concern hardware generation and will be discussed in the next chapter. The electrical structure of a design is specified with two mechanisms:

- the definition the electrical (and logical) behavior of each basic cells (the leaves of the hierarchy),

- the interconnection of these cells in blocks (the nodes of the hierarchy).

From the designer point of view, programming in **model** consists in taking basic cells from a library to build more complex structures. According to classical design methodologies (derived from standard-cell systems), the designer does not build libraries. In fact, this task is difficult because a layout, an Electrical Rule Checking interface, a transistor level description and a gate level description must be provided for each cell. One purpose of **mod2mag** is to allow the designer to build himself his own cells and libraries. That is why we describe how to specify the electrical structure of imported cells (corresponding to existing layouts). A tool (**ext2mod**) is provided for the definition of this electrical/logical structure. We also describe how to specify a behavioral model in order to follow a top-down approach in the design methodology.

In this chapter, we first explain the Electrical Rule Checking mechanism. Then we describe the generation of the simulation netlists and continue with the description of the behavioral models. We finish with the presentation of **ext2mod**, the tool which automatically derives the electrical structure of a cell from its layout. The description of the generation of router netlists will be described in the next chapter because of the topological aspects of layout.

```

Part nand2[i(0:1)] \rightarrow out

1

2

Source i

Dest out

3

4

5

. . .

6

7

End

8

Part andor[a(0:1),b(0:1)] \rightarrow \text{out}

9

Signal left, right

10

11

nand2[a] -> left

12

13

nand2[left,right] -> out

nand2[b] -> right

14

15

End

16

17

Signal select, selectbar, d(0:1), outmux

18

Source select, d(0:1)

19

nand2[select,VDD] -> selectbar

20

andor[d(0),selectbar,d(1),select] -> outmux

21

```

Table 3.1: the nand gate : the electrical specification of the IOs of the nand cell

# 3.1 Electrical Rule Checking mechanism

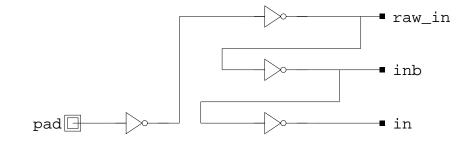

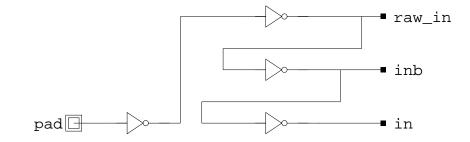

The Electrical Rule Checking mechanism checks the consistency of the connections: it detects the non-polarized inputs and the short-circuits.

This mechanism is based on the type-check of the input/output signals of the cells. Each of them cell may be declared as input or output or tristate signal.

The designer may specify these types for some cells (generally the basic ones) and let the system automatically determine the types of the IO signals of composed cells by analysing the already typed subcells.

From a theoretical point of view, only the leaves of the hierarchy need to be typed. Practically, it is better to introduce this typing mechanism at the gate level. At transistor level, source and drain of FET transistors can only be classified as tristate signals. The type of the output of a non-tristate classical gate would be found *tristate*, as the union of 2 tri-state signals. Strictly speaking, this is not false. However, this not accurate enough for the ERC to detect a short-circuit between 2 non-tristate outputs. So the best place to define the type of the IO signals is at gate-level.

The table  $3.1^1$  shows an example of the ERC interface of the nand gate.

The Source, Dest and Tristate statements follow the same syntax: Source IO-signal list

$<sup>^1\,{</sup>m The}\,\,{

m file}\,\,{

m erc}\,.{

m mod}$

The Source statement (line 2) specifies that each signal of the list is an input of the cell and must be polarized (i.e. connected to a single output or to one or more tristate signals).

The **Dest** statement (line 3) specifies that each signal of the list is an output (it may be connected only to input signals).

The **Tristate** statement specifies that each signal of the list is a tristate signal (it is sometimes a low impedance IO and can polarize input; it can be connected to other tristate signals in order to build multi-speaker buses and is not allowed to be connected to classical outputs). Power-supplies are considered as output signals.

The check is performed at each level of hierarchy and the reporting message for each error

precisely indicates the implied level of hierarchy.

At the top level of the hierarchy, the global inputs of the system are not polarized. They induce a warning report. In order to avoid this, it is possible to declare an external polarization of these global signals by a **Source** statement (line 18).

The Check is performed at the generation of simulation netlists (see below).

# 3.2 Generation of the simulation netlists

The generation of the transistor netlist is launched by the command:

model -s design

The flat netlist is written into the design.sim file. The format of this file is described in sim(5). The gate netlist is obtained in the design.log file by:

model -1 file

The format (.log) of this file is described in log(5).

For both commands, an alias file *design*.al is also generated. Its holds the synonyms for the signals.

The generation of the transistor netlist is controlled by the Output/Outputf statement, which writes into the *design* sim file. The syntax of this statement is the same as the syntax of the Message/Messagef statement:

Output list of strings and integers

or

#### Outputf "format string" list of strings and integers

The generation of the gate netlist is controlled by the Logic/Logicf statement, which writes into the *design*.log file. The syntax of this statement is the same as the syntax of the Message/Messagef statement:

Logic list of strings and integers

$\mathbf{or}$

Logicf "format string" list of strings and integers

These commands (Output/Outputf and Logic/Logicf) are very similar; their only functional difference lies in the command line flags which control them. However, the Output/Outputf command will usually be inserted in the definition of transistors while the Logic/Logicf command will lie in the definition of gates.

The table 3.2 shows a part of the file magicdef.mod (which is located in the directory ~cad/ulm/mcmos/lib8).

A signal may be known under various names; however, in the transistor and gate netlists, all the names of a given signal must be changed into an unique global name for this signal. This is done by the **Net** function, which takes a list as input and returns a list of strings representing the unique names of each signal of the list.

```

1 Part ntrans(w,1)[g] -> s,d

2 Output "n ",Net[g],Net[s],Net[d],1/50," " ,w/50," 0 0"

3 End

4

5 Part ptrans(w,1)[g] -> s,d

6 Output "p ",Net[g],Net[s],Net[d],1/50," " ,w/50," 0 0"

7 End

```

Table 3.2: definitions of nmos and pmos

At each instance of the nmos part, the netlister writes in the netlist file the line:

**n** gate source drain channel-length channel-width 0 0

which complies to the format of the transistor netlist.

# 3.3 Behavioral cell description

# 3.3.1 The aim of behavioral modeling

Behavioral modeling is necessary:

- to follow a top-down methodology. First develop the global behavior of the circuit, and step by step refine each block in sub-blocks until the gate level (which are basic cells).

- the modeling of external devices (for instance, existing integrated circuits, buses, memo-ries,...).

Behavioral modeling is the way to explain how to simulate a circuit. The behavioral description capabilities of model is compatible with the **msim** simulator (see msim(1)). It is a multimode simulator which operates at the following level :

- switch level for pass transistors.

- gate level,

- behavioral level.

During the generation of the logical netlist (the -1 option), a description of switches and gates is written into the .log by the Logic/Logicf statements, just described above. Behavioral models are written in the .beh file (see msim(1)). These two files are read by msim in order to perform the simulation.

The table  $3.3^2$  shows an example of the model for a *nand* gate. Even with a behavioral model, it is necessary to specify the type of the inputs/outputs (line 2 and 3).

The behavioral description is a list of special statements enclosed by the **Behavior** and **End** keywords (line 5 to 17).

$<sup>^2{\</sup>rm file}\ {\tt behavior.mod}$

```

1

Part nand[a,b] -> c

2

Dest c

3

Source a,b

4

5

Behavior

6

Capa 100 a,b,c

7

Slew 100 c

8

Variable va, vb, vc

9

10

Undef c

When a,b Change Do

11

12

va = Value[a]

vb = Value[b]

13

At Time + 1 NS Do

14

vc = Eval(\(va & vb))

15

16

Set c = vc

17

Done

18

Done

19

End

20

End

21

22

Signal a,b,c,d

23

nand[a,b] -> c

24 nand[c,c] \rightarrow d

25

Behavior

26

Capa 1000 c

27

End

```

Table 3.3: behavioral model of a nand

### 3.3.2 Organization of the behavioral modeling

The modeling of the behavior of a component consists of the following operations:

- the input states are read (line 12-13),

- computing a new state from the inputs states and, possibly, internal states (line 15),

- modifying of the internal state (line 15),

- modifying of the outputs (line 16),

- modeling the impedance of the inputs/outputs (line 6-7).

Flow control can be used to control the execution of the behavioral model during the simulation. This flow control is extended to specify:

- when a execution block must be awaken (line 11);

- the delay of the execution of a block (line 14).

Behavioral description requires the manipulation of expressions and the assignment of variables.

# 3.3.3 Variables

Behavioral simulation most of the time requires internal variables. These variables are declared in the **Behavior**...**End** block by the statement:

Variable *list of identifiers*

They can take any value between  $-2^31$  and  $2^31-1$  plus a special value Undef, which stands for *undefined*.

The difference between the integers and the variables lies in the step in which they are used: the integers are used during the compilation while the variables are used during the simulation.

It is possible to declare an array of variables.

# 3.3.4 Signal value acquisition

The Value function converts a list of signals into a 32 bit integer value. The argument is the list of signals: Variable v

v = Value[inputbus]

- If one of the signals is HIGHZ or UNDEF, v is assigned the Undef value.

- Otherwise, the list of signals is transformed into a list of bits by changing HIGH into 1 and LOW into 0. The list of bits is padded by 0s at the left to 32 bits if necessary. Finally the 32 least significant bits form the integer value which is returned. The first signal corresponds to the least significant bit of the result.

## 3.3.5 Behavioral expressions

Behavioral expressions consist of basic expression items and operators. The basic expression items are:

- numerical constants, possibly with a time unit PS, NS, US or MS (default is PS), a capacitance unit FF, PF, NF or UF (default is FF) or a slew rate unit PS/FF, NS/FF,... (default is NS/PF),

- integers (declared with Integer which have been changed into numerical constants),

- variables (declared with Variable which remain variable at the simulation),

- Time the current date during the simulation,

- utility functions,

- Eval function, used to evaluate early an expression (this function is useful with the schedule operator At and is described at this occasion;

- Value operator, already described in the previous subsection.

The behavioral expression operators are the same as the integer ones. The comparators has been added to these operators. They return either 0 if the comparison is true or 1 if not. The evaluation is the same. If one of the operands is undefined (set to Undef) then the results will be undefined (Undef is returned).

#### **Utility functions**

The utility functions like the variables are evaluated during the simulation. 5 functions are available:

- Random requires no argument and returns a different 32-bit value at each call (during the simulation). This function is useful to define random actions on external buses;

- Log takes a single parameter and returns the smallest integer n so that  $2^n \ge p$ . It works like the *integer* function Log but is evaluated during the simulation;

- Sqrt takes a single parameter and returns the smallest integer n so that  $n^2 \ge p$ ;

- **Open** ("filename"); this function opens the file filename in reading mode and returns a file descriptor. This action is performed at the simulation.

- Read (*fdesc*); this function reads the next integer in the file pointed by the *fdesc* descriptor. It is assumed that integers are written in decimal, one by line. If a line in the file begins with a '\*', it is treated as a comment and skipped. Open and Read are useful for instance for the initialization of of a ROM.

An utility procedure can be added to these function. The **Close** takes a single parameter and closes the file associated with this parameter.

### 3.3.6 The modification of signals

When the behavior has been calculated, the simulator must diffuse the result in the output signals of the part. This can be performed using the following statements:

- 1. Undef signal list. The value of these signals are set to undefined state (example on line 10).

- 2. HighZ signal list. The value of these signals are set to high impedance state.

- 3. Low signal list. The value of these signals are set to the low level (0V).

- 4. High signal list. The value of these signals are set to the high level (5V).

It is also possible to change the state of a bus according to the binary value of a variable: There is another way to change the value of a bus:

**Set** signal list = expression

If the expression value is Undef, every signal of the list is set to Undef. If the expression has an integer value v, the  $n^{\text{th}}$  signal is set to high (resp. low) if the  $n^{\text{th}}$  bit of the binary representation of v is 1 (resp. 0). The least significant bit of v corresponds to the first signal of the list.

# 3.3.7 The modeling of the inputs/outputs

If nothing else is specified, inputs and outputs of the part are supposed to be perfect:

- no parasitical capacitances on inputs/outputs,

- null output impedance.

It is possible to add a capacitance to a signal or a signal list with the statement: Capa capacitance signal list

The capacitance is added for every signal of the signal list.

It is possible to specify an impedance for each signal statements. For instance, Slew impedancesignal list

associates the signal list a delay equal to the product of the capacitance of each node with *impedance*. The value of the impedance is expressed in pS/pF.

# 3.3.8 The modeling of a multitalker bus

We must describe what happens when 2 different modifications of state are applied to the same signal. These modification are never applied simultaneously because of the sequential organization of the simulator. Two desired effects are possible:

- The two modifications belong to the same object. The new state modification must override the old state. For instance, a clock generator sets and resets the clock at each period.

- The two modifications belong to different objects. These objects will be in conflict on the output.

In order to offer naturally the 2 possibilities to the designer, each signal modification statements is associated with the current part instance. Each modification statement changes the state of the output pole associated with the current part instance. Modification statements associated with different part instances modify the states of different output poles. Each output pole has a current state and an impedance. Every Output poles corresponding to the same signal will be used by the simulator to compute the state of the signal, as it is done for electrical gates.

# 3.3.9 Debugging functions

For debugging purpose at simulation time, it is possible to print a message with the commands **Print** and **Printf**. They work like **Message** and **Messagef**.

## 3.3.10 Scheduling flow control

Two new statements are used to describe the behavior of a circuit:

- When instructs the simulator to execute a statement list on every specified transition on some signals,

- At postpones the execution of some statements.

These features are not easy to understand because of the parallelism they may hide. The next example describes the behavior of a Read-Only-Memory.

```

1 Part tms2732A_17[a(0:11),eb,gb] -> d(0:7)

2

3 Source a,eb,gb

4 TriState d

5 Signal m(0:7),on

```

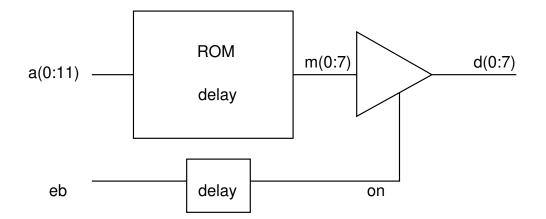

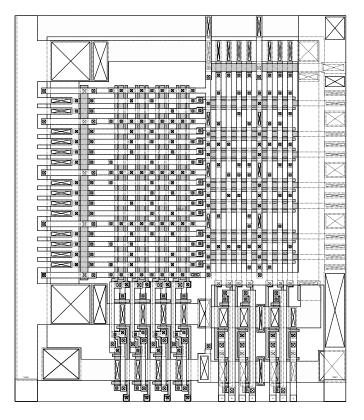

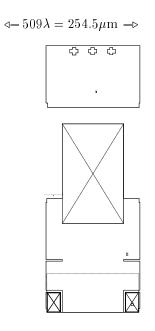

Figure 3.1: organization of behavioral description of the ROM

```

6

Integer ta, ten

Constant size = 1 << 12

7

8

9

Behavior

10

Capa 9 PF a,eb

Capa 20 PF gb

11

Capa 12 PF d

12

Slew 60 PS/FF d

13

14

15

Variable rom(0:size-1)

16

Variable i,f,date

17

f = Open("program.rom")

18

19

For i=0:size-1 Cycle

rom(i) = Read(f) & 255

20

21

Repeat

22

Close(f)

23

Undef m

24

25

When a Change Do

26

Undef m

27

28

date = Time

29

At Time + 170 NS Do

30

If Time = date + 170 NS Then

31

32

Set m = rom(Eval(Value[a]))

33

Endif

34

Done

35

Done

36

37

```

```

38

When eb Low Do

39

At Time + 60 NS Do

40

Set on = 1

Done

41

42

Done

43

Set on = 0 When eb High

Undef on When eb Undef

44

45

When m,on Change Do

46

47

Switch Value[on]

48

Case 1

49

Set d = Value[m]

50

Exit

51

Case O

52

HighZ d

53

Exit

54

Default

55

Undef d

56

End

57

Done

End

58

59

End

```

Behavioral statements which are not contained to a When block, are evaluated during the initialization phase of the simulation. These statements are the initialization of the behavioral model for the part (lines 10-22).

The array of variables **rom** will contain the values of the words of the ROM. It is loaded from a file during the initialization of the simulation (line 18-22).

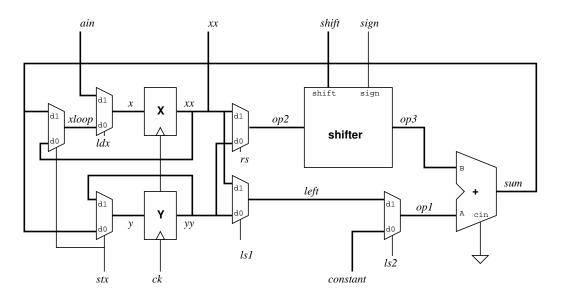

We then describe the actions to be taken on given events (with the When operator). As it is easier to describe separate automata for separate functionalities, we have divided the description of the ROM is 3 parts (fig. 3.1):

- the ROM itself with its delay (line 26–35),

- a delay on the enable (eb) (line 38-48),

- the delayless tristate buffer (line 50-61).

#### The When operator

The When operator is used to trigger an action on each occurrence of a given event.

The syntax of this statement is:

When signal list <transition> Do statement list

### Done

or the abbreviate one:

statement When  $signal\ list$  transition

<transition> is one of the following keywords:

- Undef : the statement list is executed at every end of transition to the Undef state.

- HighZ : the statement list is executed at every end of transition to the HighZ state.

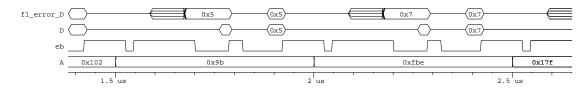

Figure 3.2: wave-forms of the ROM

- Low : the statement list is executed at every end of transition to the Low state.

- High : the statement list is executed at every end of transition to the High state.

- Change : the *statement list* is executed at every end of transition of any kind of the *signal list*.

For instance (line 43) the Set statement is executed each time the signal eb reaches the state High.

#### The At operator

To simulate delays, we need to postpone the execution of actions using the At operator. The syntax of this statement is:

At expression Do statement list

#### Done

or the abbreviate one:

statement At expression

The statement list is executed at absolute time given by *expression*, expressed in picoseconds. The **Time** keyword which represents the current time during the simulation is used to transform a delay into an absolute time.

When the delay is elapsed, the action is executed. It generally needs variables and states of signals. A serious problem is to choose whether to take the values of the variables and signals before the delay or after. By default the evaluation occurs after the elapsed delay.

Suppose (fig. 3.2) that eb is set to 0 at time  $t_0$  and set at time  $t_1 < t_0 + 60$ ns. Then at  $t_1$  on is set to 0 and later at  $t_0 + 60$ ns on is set to the opposite of the value of eb at time  $t_0 + 60$ ns: 0. So nothing happens.

On the opposite, if we replace the line 40 by

Set on = Eval(\Value[eb])

the expression is evaluated at time  $t_0$  with the value 1. At time  $t_1$ , on is set to 0. At time  $t_0 + 60$ ns, on is set to 1.

In this example, the first choice is the good one. But it is not the case if we need to simulate a pipe which replays with a given delay everything that comes in:

When in Change Do

Set out = Eval(Value[in]) At Time + 10 NS ne

Done

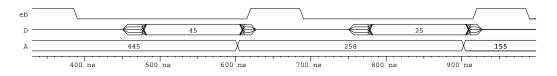

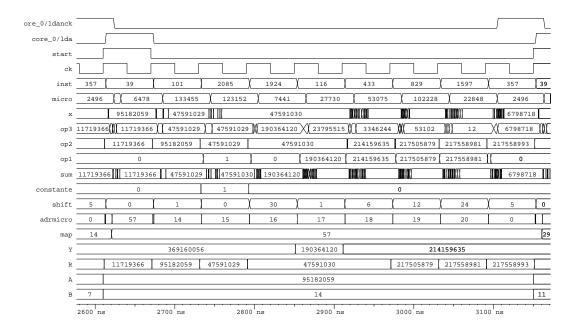

Figure 3.3: wave-forms of the ROM

Here the Eval functions is necessary when the delay between two changes may be smaller than 10 ns.

Glitches are the source of our problem. Sometimes we want to specify that the result is available after a delay during which the inputs are steady. The behavior model needs to check that no transition has occurred since a given time (line 31).

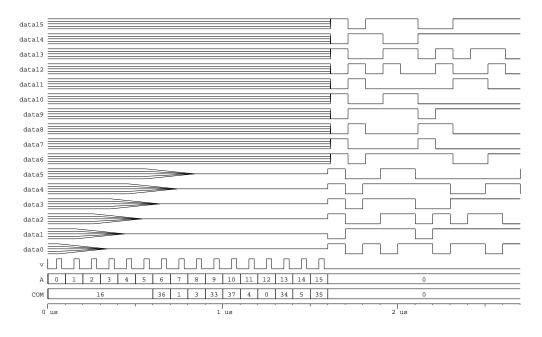

The figure 3.3 shows the wave-forms of the simulation.

## 3.4 Ext2mod: an automatic cell characterization

The major problem of a library is its reliability. To provide a complete interface for a layout library we must provide for each cell the following information:

- the layout,

- the model input/output interface,

- the Electrical Rule Checking interface,

- the transistor level description,

- the gate level description,

The description of the layout aspect consists in a .mag file (see magic(5)) while the rest of the information is contained in the associated model function. The purpose of ext2mod is to automatically derived from the extracted netlist file .ext associated to the layout file the model description of the file. Creating a new cell proceeds in the following steps:

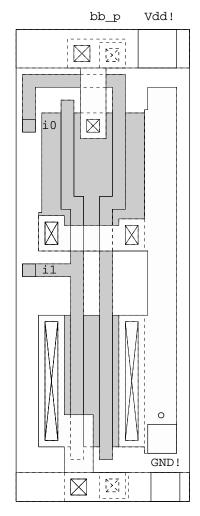

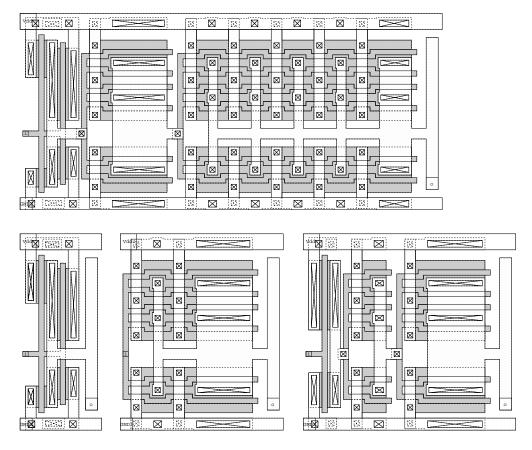

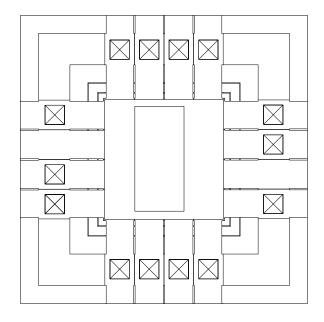

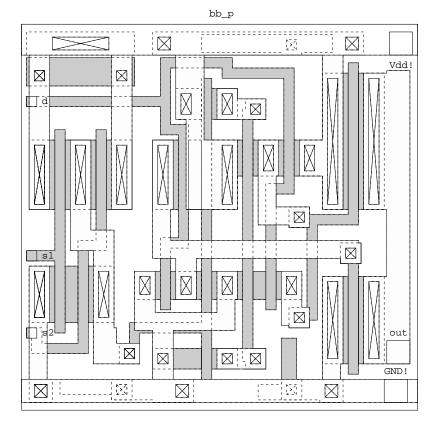

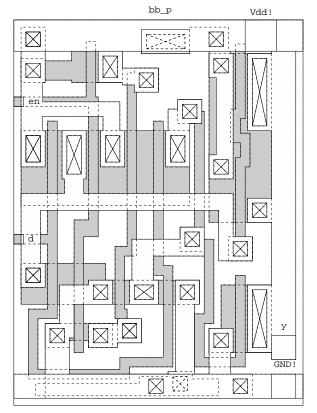

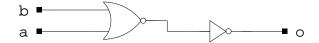

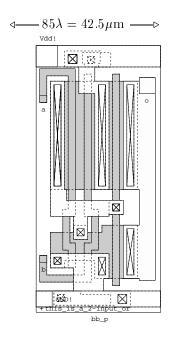

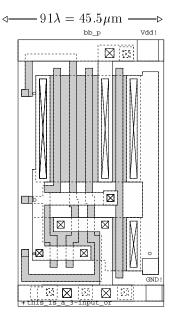

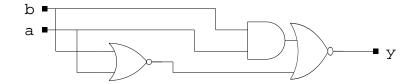

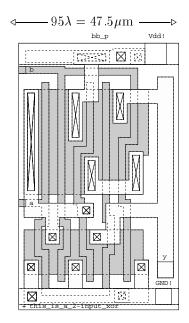

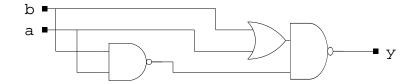

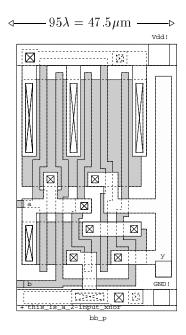

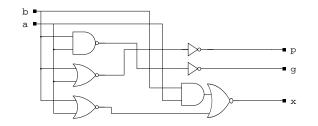

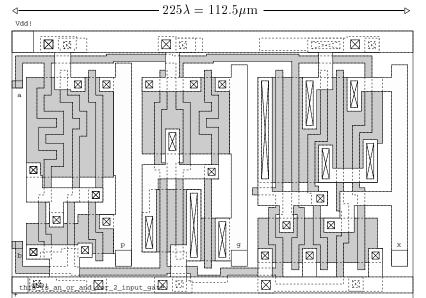

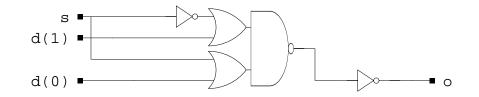

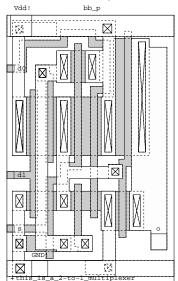

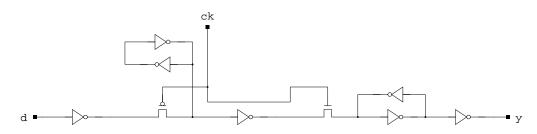

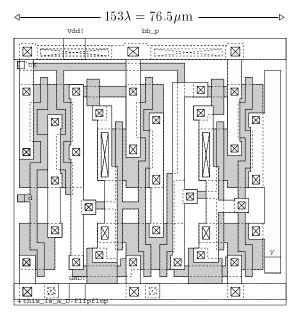

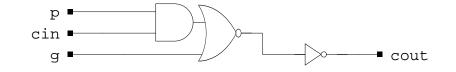

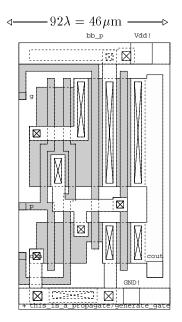

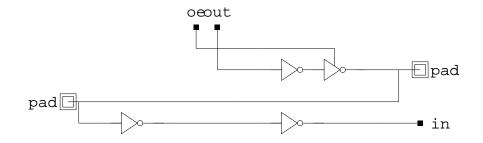

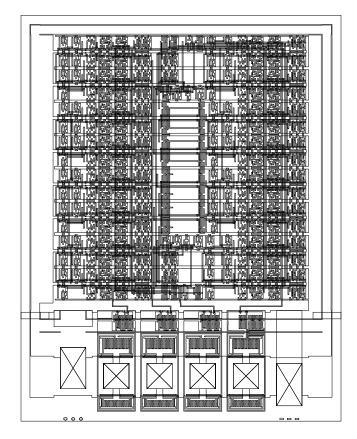

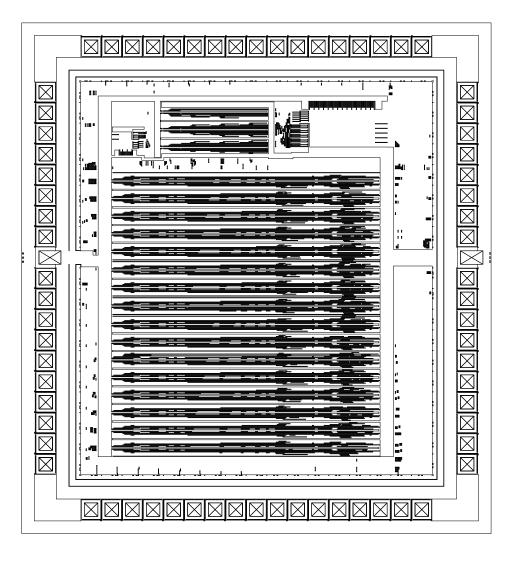

- the design of the layout with **magic** (creation of *cell.mag* see layout in figure 3.4 and file nand2.mag),

- the extraction of the hierarchical netlist with **magic** (creation of *cell.ext* see file nand2.ext),

- the generation of the model description by the command: ext2mod cell

(creation of *cell.mod* see table 3.4) and file nand2.mod).

**Ext2mod** detects the input/output signals of the cell (line 1). In order to reserve simple names to generic part of **model**, cells imported from **magic** are identified with their **mag\_** prefix.

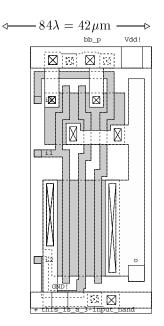

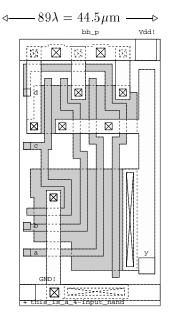

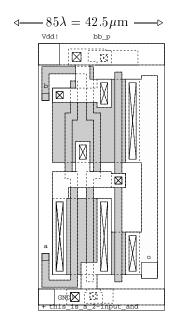

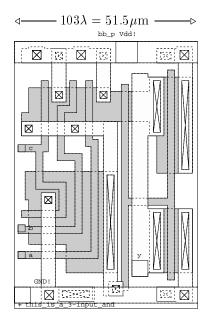

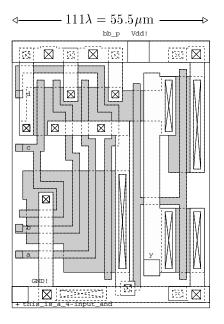

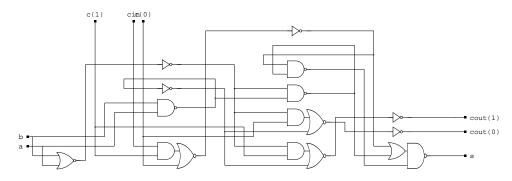

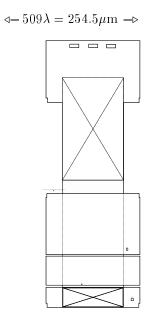

Figure 3.4: layout of the nand2 gate

The transistor level description of the layout of the nand gate is shown at lines 5–14. Parasitic capacitances and transistors are defined and interconnected.

The Electrical Rule Checking interface is defined for the input/output signals at lines 17–18. The gate level description takes place at lines 19–21. Parasitic capacitances and logical gates are defined and interconnected. A timing model is directly derived from the size of the transistors and the capacitors. Delays are defined in ps and fanout are defined in ps/pF. This *nand* has the following characteristics:

- an intrinsic delay of 586 ps on each input,

- an additional delay of 3138 ps for every 1 pF connected to the output,

- a 0.095 pF load capacitance on each input.

```

MagicPart mag_nand2 [i(0:1)] -> o

1

2

{ transistor description }

3

Signal 1_0

4

Output "C ",Net[Vdd]," GND 35"

5

Output "C ",Net[o]," GND 74"

6

Output "C ",Net[i(0)]," GND 7"

7

8

Output "C ",Net[i(1)]," GND 5"

9

Output "C ",Net[1_0]," GND 17"

Output "C ",Net[GND]," GND 24"

10

Output "p ",Net[i(1),o,Vdd],"2300 200 0 0"

11

Output "p ",Net[i(0),Vdd,o],"2350 200 0 0"

12

Output "n ",Net[i(1),GND,1_0],"2050 200 0 0"

13

Output "n ",Net[i(0),1_0,o],"2050 200 0 0"

14

15

{ logic description }

16

17

Dest o

18

Source i(0), i(1)

Logic "cap ",Net[i(0)],95

19

Logic "cap ",Net[i(1)],92

20

21

Logic "nand ", Net[o], " 3138 ", Net[i(0)], " 586 ", Net[i(1)], " 586 "

22

23

End

24

```

Table 3.4: electrical description of the nand6 gate generated by ext2mod

### 3.4.1 Layout optimization

The -f option of ext2mod generates feed a magic command file which can be used while editing the cell. The command:

:source feed

executes this file. It defines some feedbacks which indicates some information on the transistors. It helps to scale the n/p-transistors. If the *p*-transistor path of a gate is to weeak, transistors responsible for this fact will get feedbacks to announce the problem associated with the scale required to adapt it.

## 3.4.2 Automatic documentation

The -t option of ext2mod generates a data sheet associated with the cell. The next page shows the data sheet automatically generated by the command:

ext2mod -t nand2; latex nand2; dvips nand2.

The appendix D has been automatically generated by ext2mod. For more details about this program, see ext2mod(1).

As we have now defined how to import layouts into the system, it is time to learn how to build bigger layout structures with **mod2mag**. This is the subject of the next chapter.

Memos

## Cell Nand2: a 2-input nand

## MagicPart mag\_nand2 [i(0:1)] -> o

## Inputs and Outputs

|        | Outputs                                  | 0             |

|--------|------------------------------------------|---------------|

|        | $\Delta t / \Delta C \ (\mathrm{ns/pF})$ | 2.82          |

| Inputs | Capacitance                              | $\Delta t$ ns |

| i(0)   | $0.09 \ \mathrm{pF}$                     | 0.54          |

| i(1)   | $0.09 \ \mathrm{pF}$                     | 0.54          |

Description

## Chapter 4

## Hardware Generation

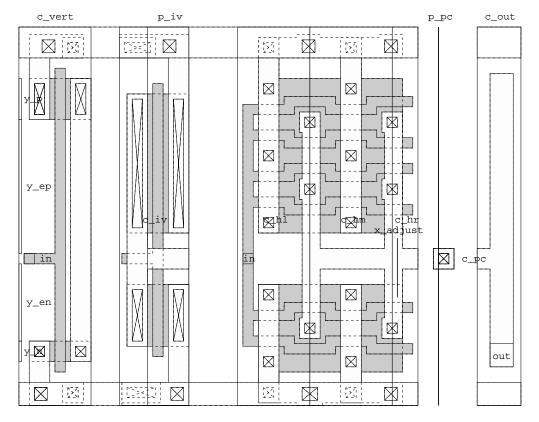

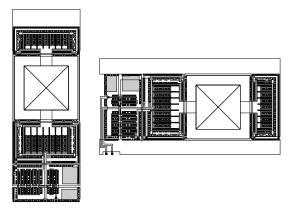

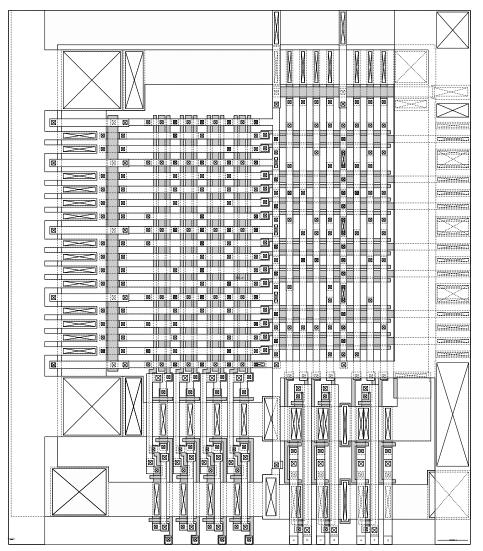

This chapter is the occasion to discover the different styles of hardware generation. We will discover:

- the use of external layouts,

- the tessellation of layouts,

- the generation of a basic cell,

- the generation of a macro-cell,

- the data-path generation,

- the chip finishing,

- the generation of pcb data.

Every declared part may contain the information on the way to build its layout. The style of this building is specified by replacing the "Part" keyword by one of the following:

- Part: this is only a method for building the hierarchy. No Layout will be generated: it will be the responsibility of the calling parts. Part is a macro with parameters.

- MagicPart specifies that the part is an imported cell. Its layout must already exist.

- PadPart specifies that the part is an imported pad cell. Its layout must already exist.

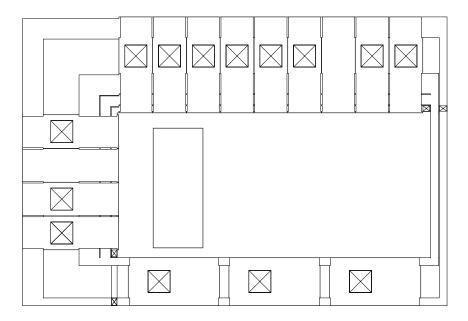

- PavePart specifies that the layout is built by tessellation of the layouts of subcells.

- BlockPart specifies that the part is a compiled data-path.

- ChipPart specifies that the part is a whole circuit with pads.

- PcbPart specifies that the part is a whole board.

MagicPart, PadPart, PavePart, BlockPart are involved in with layout generation (.mag files). The command:

model design -m

generates the layout files. ChipPart and PcbPart are concerned by Pcb data generation. The command:

model design -p

produces theses data.

Some of these styles (PavePart and ChipPart) are only placement operators: the electric connectivity is not guaranteed and is assumed to be achieved by the placement itself. No routing is performed by mod2mag. This is the reason why, an associated netlist is generated in the .net format of magic(see net(5)). It is possible to use the router of magic to draw these interconnection (see the example of the section 4.6, for the chip finishing).

We will discover in this chapter these different layout generation styles.

## 4.1 Importing external layout

It is necessary to provide a way to import layouts, in order to get:

- basic pieces of layouts to assemble them,

- complex and hierarchical pieces of layouts designed using other CAD-tools (it allows a bridge with external tools).

If the layout of a part is directly imported, it is specified through the keyword MagicPart for general cells and PadPart for pad cells which must be located at the periphery of the chip. Therefore we can directly use the model description given by ext2mod.

When the software needs to generate the layout of the part mag\_nand2, it simply uses the one accessible in the file named nand2.mag.

A pleasant way to use the file generated by ext2mod is to include it (the Include command). This will be very flexible in case of modification of the layout. Everything can be recompiled thanks to a makefile mechanism.

To avoid the proliferation of very small tile files required to describe the various parts of layout, it is possible to gather them in a layout library. The statement

#### Magiclib "layoutlib"

declares the name of a layout library located in *layoutlib*.mag.

It is also possible to declare zones in the layout (using the labels  $x_param$  and  $y_param$ ) that will be stretched depending on the value of integer parameters (*param*) in the **model** description of the part.

The layout library and the zone stretch mechanisms are detailed in the section describing how to build a basic cell.

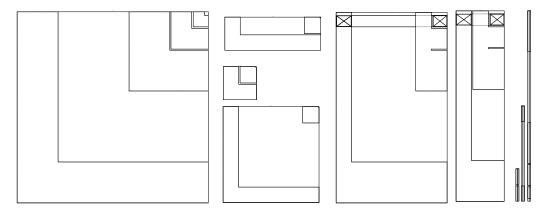

## 4.2 Tessellation of layout

As we know how to call basic pieces of layout, it is time to learn how to build composed layouts.

The most simple way of building layout consists in putting different layout tiles together. The resulting building is a tessellation of layouts. This style of generation does not deal with electrical connections (nonetheless, they can be performed by side effects). It consists in putting side by side the different pieces. This style is specified while declaring a part. The use of the keyword **PavePart** instead of **Part** indicates that the tessellation style is desired for the generation of the layout of that part.

The structure of a layout building is hierarchically described with constructors. It follows the natural hierarchy given by the **Part** instance mechanism. It is also possible to structure the layout inside a part definition using the following constructors:

- placement constructors (Xplace, Yplace and Yplace/Pile),

- transformation operators (Xmirror, Ymirror, Rotate90, Rotate180 and Rotate90).

## 4.2.1 Placement constructors

The Placement constructors are used as soon as a topological placement is required for the layout generation or for the PCB generation. The placement constructors follow the syntax:

```

Xplace { or Yplace or Zplace or Pile }

```

statements End

statements.

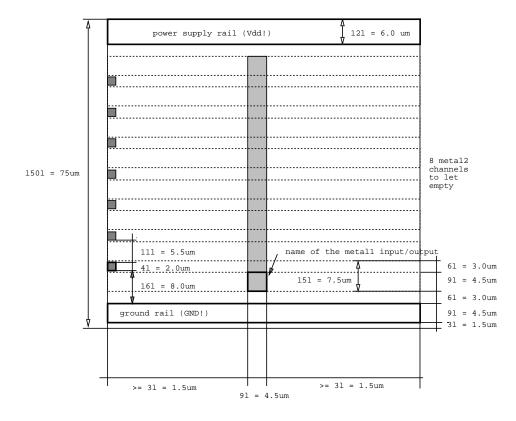

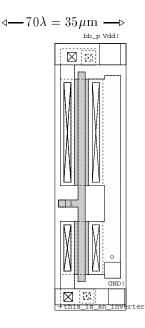

#### **Reference** rectangle

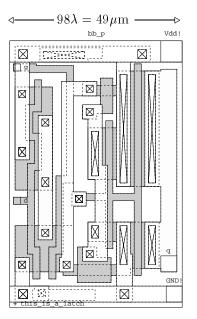

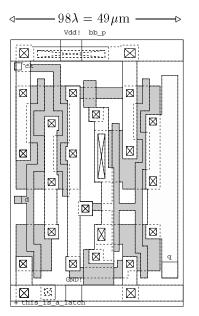

A geometric support is required to achieve the tessellation. The geometrical support is a rectangle (called *reference rectangle*) which roughly defines the occupied place of the layout. In an imported layout, this rectangle is specified by a label (see **magic** (5)) named **bb\_p**. This label can be observed in the layout of the **nand2** cell (figure 3.4, page 37). If this label does not exist in the layout, the effective bounding box is used. Often the desired rectangle fits the bounding box, the label is then optional. In a composed layout (built with the tessellation constructors, or other constructors to be defined), the rectangle is the bounding box of the set of reference rectangles of the constituting layouts.

This rectangle is the only topological information used by the layout generator. The effects of the constructors are directly drawn from these rectangles. It is now possible to describe the constructors.

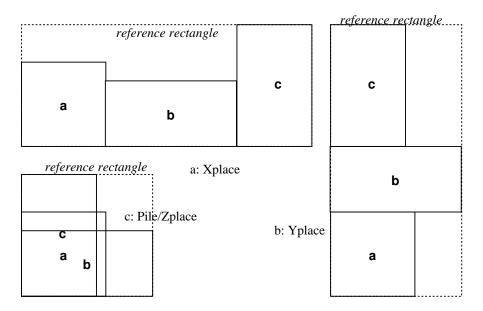

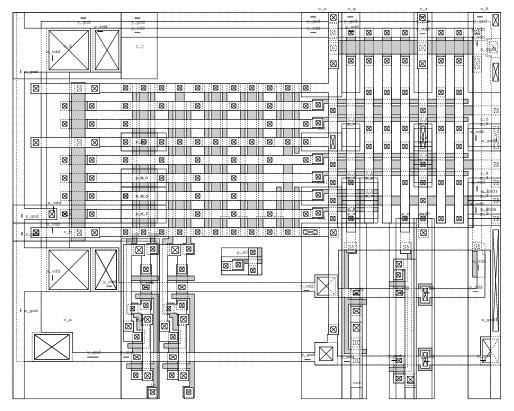

**Xplace** concatenates the constituting instances in the order of their interpretation, from left to right, in a way that the lower-right corner of the reference rectangle of an instance fits the lower-left corner of the reference rectangle of the next instance. The figure 4.1.a shows an example of an X-axis style concatenation.

**Yplace** concatenates the constituting instances in the order of their interpretation, from the bottom to the top, in a way that the upper-left corner of the reference rectangle of an instance fits the lower-left corner of the reference rectangle of the next instance. The figure 4.1.b shows an example of an Y-axis style concatenation.

**Pile** or **Zplace** piles all the constituting instances on top each other in a way that the lowerleft corners of the reference rectangle of each instance are located at the same point. The figure 4.1.c shows an example of piling up style. This operator is very useful for customizing a

Figure 4.1: examples of the constructors

| keyword   | transformations           |

|-----------|---------------------------|

| Xmirror   | symmetry - x              |

| Ymirror   | symmetry - y              |

| Rotate90  | rotation by 90°           |

| Rotate180 | rotation by 180°          |

| Rotate270 | $rotation\ by\ 270^\circ$ |

Table 4.1: transformation operators

cell with vias or contacts. A tile contains the major part of the layout, while other tiles are the personalization of the layout with small connections. For instance, it is useful for decoders.

While the constructors specify the concatenation axis, the transformation operators is useful to change the orientation of the part of a layout.

## 4.2.2 Transformation operators

The syntax of these operators is the same as the one of the constructors:

```

<Transformation operator>

statement(s)

```

End

The operators applies to the statement(s) which is(are) between itself and the End statement. The table 4.1 summarizes those different operators.

Two examples will illustrate the capabilities of the tessellation style with their operators. The first one will show how to build a basic parametrical cell and second one will show how to build macro-cell.

These examples will be the subject of the next two sections.

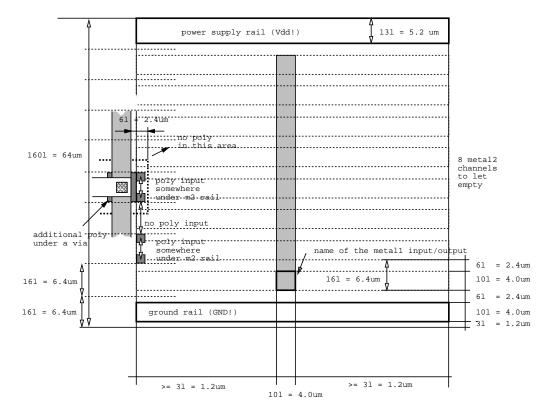

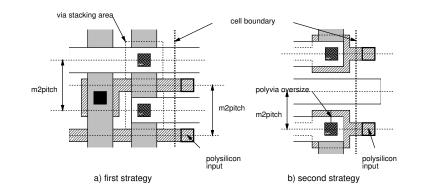

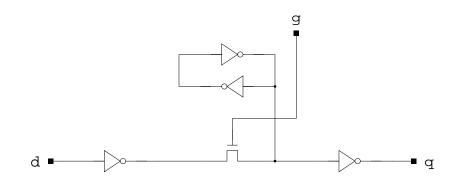

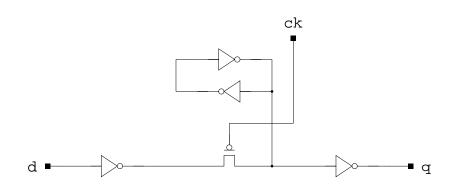

## 4.3 The building a basic cell

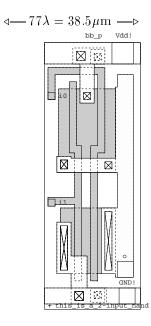

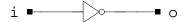

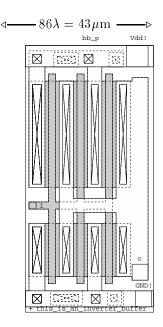

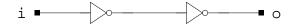

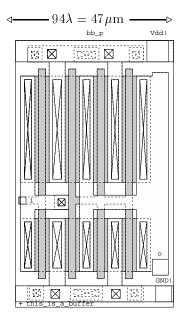

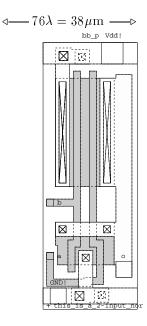

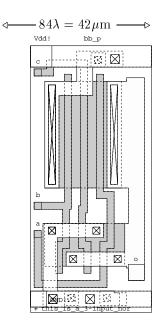

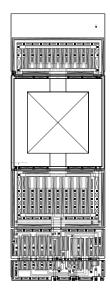

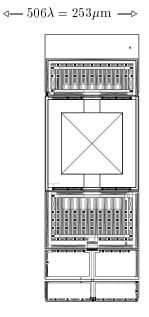

In this section we illustrate the use of the tessellation style for basic cells. As this style is adequate with transistors sizing, we have chosen to design a parametrical inverting buffer. This buffer will be speed optimal. All the files involved in this example are available in the directory "cad/ulm/mcmos/lib8.

## 4.3.1 Speed of a CMOS inverting driver

The purpose of a driver is to amplify a weak signal to distribute it on a heavily loaded wire. A basic inverter can be characterized by:

- its input capacitance C (expressed in pF), proportionnal to the  $W \times L^1$  area of the gates of the transistors,

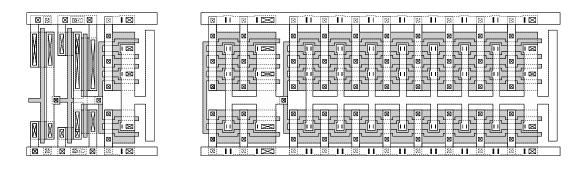

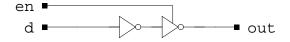

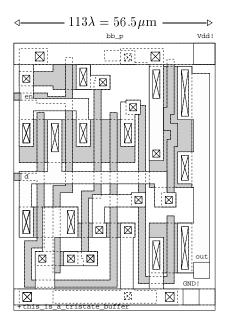

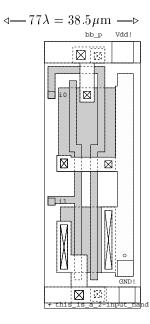

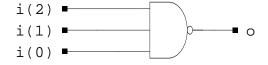

- its output impedance R (expressed in ns/pF), proportionnal to the form factor  $\frac{W}{L}$  of the transistor gates.